Physical Implementations of Qubits

Superconducting Qubits — IBM Nighthawk & Google Quantum Echoes

IBM Nighthawk and the Road to Quantum Advantage

IBM's Nighthawk processor, released to IBM Quantum cloud users in January 2026, represents the current state of the art in superconducting quantum computing. Its 120 qubits connect via 218 next-generation tunable couplers in a square lattice — 20% more connectivity than its predecessor Heron. This allows circuits 30% more complex to run at low error rates, enabling algorithms with up to 5,000 two-qubit gates. IBM projects 7,500 gates by end of 2026 and 10,000 by 2027, with 1,000+ qubit modular systems using long-range couplers planned for 2028.

The Loon companion chip (also announced November 2025) is a smaller 112-qubit experimental processor that validates all the hardware elements of fault-tolerant quantum computing: multi-layer routing, long-range couplers for distant qubit connections, and fast qubit reset circuits. Together, Nighthawk and Loon represent IBM's near-term and long-term quantum strategy respectively. IBM's classical error syndrome decoder — implemented on an AMD FPGA — now processes error syndromes in under 480 nanoseconds, a 10× speedup over previous approaches and one year ahead of schedule.

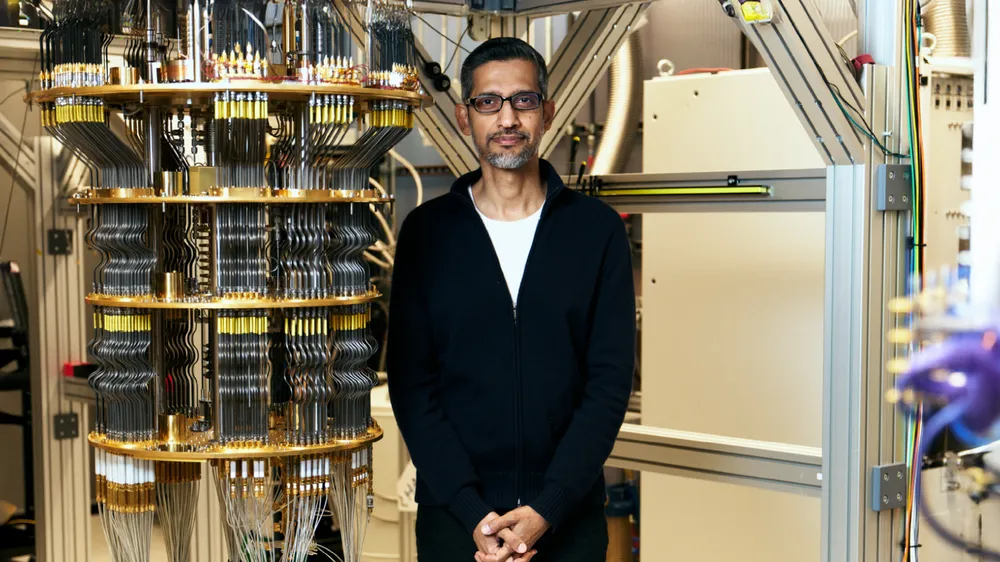

Google Quantum Echoes (October 2025) was the first demonstration of verifiable quantum advantage: the Willow chip ran the Quantum Echoes algorithm (out-of-time-order correlators) 13,000 times faster than the best classical supercomputers on a computation that is independently verifiable on another quantum device. Unlike the 2019 Random Circuit Sampling benchmark — which produced outputs with no direct scientific value — Quantum Echoes measured molecular geometry in collaboration with UC Berkeley researchers, demonstrating that quantum computation can produce useful, reproducible, real-world results. Google's Willow array delivered single-qubit fidelity of 99.97%, two-qubit fidelity of 99.88%, and readout fidelity of 99.5% across all 105 qubits simultaneously.

Google's Two-Track Strategy: Superconducting + Neutral Atoms

On March 24, 2026, Google Quantum AI announced it is expanding beyond superconducting qubits to include a neutral atom quantum computing program, led from a new lab in Boulder, Colorado. The strategic rationale — stated by Hartmut Neven — is that superconducting processors excel at scaling in the time dimension (circuit depth, gate speed) while neutral atoms excel at scaling in the space dimension (qubit count, connectivity). Running both programs allows Google to cross-pollinate research breakthroughs and deliver platforms suited to different problem types. This is a significant development: Google's decade-long exclusive focus on superconducting qubits had made it an outlier; IBM, Microsoft, and most academic groups had already been exploring multiple qubit modalities.

Why neutral atoms are attracting investment: QuEra and collaborators demonstrated in 2025–2026 that neutral-atom architectures can achieve 50–100× speedups over what was previously thought possible, by exploiting the platform's unique reconfigurability and long coherence times. Neutral-atom arrays of 6,100+ atoms have been demonstrated with 99.98% single-qubit fidelity — combining ion-level coherence with photonic-level scalability.

Trapped-Ion Qubits — The Fidelity Leader

Quantinuum Helios and Oxford Ionics: Record Fidelity in 2025

Quantinuum's Helios system (November 2025) is the current commercial benchmark for trapped-ion performance. Its 98 barium-137 ions achieve 99.92% two-qubit gate fidelity and 99.95% SPAM (State Preparation and Measurement) fidelity — an order of magnitude improvement in error rate over IonQ's Forte system. The QCCD (Quantum Charge-Coupled Device) architecture physically moves ions between dedicated memory, cache, and logic zones on chip, enabling all-to-all connectivity without the SWAP overhead that plagues fixed-topology superconducting chips.

The 48 logical qubit milestone: In 2025, Helios demonstrated 48 error-corrected logical qubits at a 2:1 physical-to-logical qubit ratio — a remarkable reduction from the ~1000:1 ratio required by surface codes. This was enabled by Quantinuum's QLDPC codes and real-time GPU-accelerated error correction via NVIDIA GB200 integration. Quantinuum set a quantum volume record of 33,554,432 — meaning the system can reliably execute random circuits across 25 qubits with 50%+ success probability.

Oxford Ionics (2025) reached 99.99% two-qubit gate fidelity — the highest reported for any qubit platform commercially. Their approach uses microwave-driven gates rather than laser gates, removing the need for precise optical alignment and making the system more manufacturable. IonQ's fifth-generation Tempo system (100 qubits) entered commercial service in 2025, with a 256-qubit sixth-generation system planned for Q4 2026 targeting 1,600 fault-tolerant logical qubits on its long-term roadmap.

Neutral Atom, Photonic, and Topological Platforms

Neutral Atoms — 2026's Breakout Platform

Neutral-atom arrays in optical tweezers have scaled to 6,100+ atoms with 99.98% single-qubit fidelity (2026 benchmark). QuEra and collaborators demonstrated 50–100× circuit speedups by exploiting reconfigurability and long coherence. Google's March 2026 entry into neutral atoms confirms the platform's maturity. Microsoft's Magne system — combining Microsoft QEC software with Atom Computing's neutral-atom hardware — is under construction in Denmark, targeting deployment by late 2026 as the world's first operational logical-qubit machine.

Photonic — Long-Range Vision

PsiQuantum announced Omega in January 2025 — a silicon-photonic chipset architecture for million-qubit systems using standard semiconductor fabs. Xanadu's Borealis (216 modes, 2022) remains the photonic benchmark for quantum advantage demonstrations. Photons do not decohere and operate at room temperature, but deterministic two-qubit gates remain the unsolved challenge. PsiQuantum has raised over $1.3 billion on the thesis that silicon photonics manufacturing can solve the scalability problem no other platform can.

Topological — Contested but Consequential

Microsoft unveiled Majorana 1 in February 2025: 8 topological qubits using Majorana zero modes in indium arsenide/aluminum nanowires, with a roadmap to a 27×13 tetron array. The long-term target is one million qubits on a single chip with inherent error resilience from topological protection. However, Nature's own reviewers stated the published paper does not constitute evidence for Majorana zero modes, and a 2025 Australian preprint raised decoherence objections. Microsoft disputes these challenges. The DARPA US2QC program is funding Microsoft's fault-tolerant prototype.

AWS Cat Qubits — The 90% Overhead Reduction Claim

AWS's Ocelot chip (2025), based on cat qubits — superpositions of coherent states in superconducting oscillators — demonstrated bit-flip times approaching one second, over 1,000× longer than conventional superconducting qubits. Cat qubits biased toward one error type allow asymmetric error correction codes that use far fewer physical qubits per logical qubit. AWS claims up to 90% reduction in error-correction overhead compared to surface codes. Ocelot has 5 data qubits, 5 buffer circuits, and 4 ancilla qubits — too small for computation but a compelling proof of concept for fault-tolerant architecture.

The Scalability Challenge — Physical vs. Logical Qubits

The Five Scalability Challenges

What Stands Between Today's Hardware and Cryptographic Relevance

1. Decoherence: All qubit types lose their quantum state through environmental interaction. IBM Nighthawk's 350 μs T1 is a 3.5× improvement over Willow, but fault-tolerant algorithms require executing millions of gate cycles. Trapped-ion seconds-long coherence times set the current ceiling.

2. Error rates and the fault-tolerance threshold: The surface code threshold is ~1% physical error rate. Google's Willow crossed the below-threshold regime in December 2024, demonstrating exponential error suppression from 3×3 to 7×7 arrays. IBM's Nighthawk/Loon combination is targeting the same milestone with improved LDPC codes. Quantinuum Helios's 99.92% two-qubit fidelity (0.08% error) already operates well below threshold.

3. Qubit overhead for error correction: The IBM LDPC breakthrough (Nature 2024) demonstrated 12 logical qubits from 288 physical qubits — a 24:1 ratio vs. the ~1000:1 of surface codes. Quantinuum Helios achieved 48 logical qubits from 98 physical for memory. However, these achievements are for quantum memory; fault-tolerant computation with logical gate operations remains harder and is still being demonstrated.

4. Control system scalability: IBM's move to 300mm wafer fabrication has doubled R&D speed. But scaling from hundreds to millions of qubits requires cryogenic control electronics inside the dilution refrigerator, microwave packaging that avoids crosstalk, and classical decoder hardware capable of processing error syndromes in real time. IBM's AMD FPGA decoder achieving 480 ns syndrome processing is a key milestone for this problem.

5. The cryptanalytic gap: A fault-tolerant Shor's algorithm for RSA-2048 requires ~4,000 logical qubits and ~4 million physical qubits running at high fidelity for several hours. Today's machines are at 98–120 noisy physical qubits. The transition requires not just more qubits but a complete architectural shift to error-corrected logical qubits — a multi-step engineering programme expected to take until the early-to-mid 2030s under optimistic trajectories.

Implications for Cryptographic Security

The 2026 Picture: Progress is Real, But the Gap Remains Large

Google's October 2025 Quantum Echoes milestone and IBM's 2026 quantum advantage target represent genuine scientific progress, not hype. The field has moved from theoretical demonstration to verifiable, reproducible, scientifically useful computation. However, it is important to distinguish what these milestones mean for cryptography: Quantum Echoes ran a 65-qubit subsystem of Willow on a physics simulation task. Shor's algorithm on RSA-2048 requires ~4,000 error-corrected logical qubits. The gap is approximately four orders of magnitude in logical qubit count, plus the full engineering stack for fault tolerance.

The timeline consensus is tightening: In 2025–2026, multiple credible organisations — IBM (2029 fault tolerance target), Google, and Quantinuum — have given specific timelines for fault-tolerant quantum systems. The broad industry consensus has shifted from “decades away” to “late 2020s to early 2030s for first commercially useful fault-tolerant systems.” Cryptographically relevant systems — capable of running Shor's algorithm at scale — follow after that, likely mid-2030s under optimistic assumptions.

Harvest Now, Decrypt Later: Even though current quantum hardware cannot break RSA, adversaries may be recording encrypted traffic today to decrypt it once a capable quantum computer exists. Data with long secrecy requirements — classified communications, medical records, financial transactions, intellectual property — is already at risk from this strategy. NIST finalised the first three PQC standards in August 2024 (ML-KEM, ML-DSA, SLH-DSA) and added HQC as a backup KEM in March 2025. Migration should be underway now.

Resources & Further Reading